|

|

|

|

| Z800CPUにはユーザモードとシステムモードの2種類の動作モードがあります。ユーザモードでは実行できない命令やアクセスできないレジスタがいくつか存在します。通常、ユーザモードはアプリケーションプログラムに使用されることになります。システムモードではすべての命令が実行でき、すべてのCPUレジスタがアクセスできます。このモードはOSを動作させる際に有効です。CPU資源の分割は、システム保全をより完璧なものにしてくれます。なぜなら、ユーサモードで走るプログラムを、システムインタフェースのイベントに関する処理から隔絶できるからです。WindowsNTやWindowsXPがアプリケーションの暴走に対して強固である理由がこれです。 |

| さらに、この2つのモードをサポートするために、2本のスタックポインタが用意されています。1本はユーザスタック、もう1本はシステムスタックと呼びます。これら2つのスタックは、割り込みやトラップが発生したときの複雑なタスクの切り替え処理の負担を軽減してくれます。ユーザスタックをシステム情報から切り離すために、割り込みやトラップの発生でセーブされるべき情報は、常に新しいプログラムステータスがロードされる前にシステムスタックにプッシュされます。 |

|

|

|

| Z800CPUのアーキテクチャは、4種類のアドレス空間をサポートしていますが、これらはそれぞれ異なった形式でアクセスされます。以下にその4つのアドレス空間を示します。 |

|

|

CPUレジスタ空間 |

|

|

CPUコントロール&ステータスアドレス空間 |

|

|

メモリアドレス空間 |

|

|

I/Oアドレス空間 |

|

| CPUレジスタ空間 |

CPUレジスタ空間とは、CPUレジスタファイル中の全レジスタのことです。CPUレジスタはデータやアドレスの操作に使用されるものですが、そのアクセスに関しては各CPU命令(インストラクションセット)ごとに決まっています。CPUレジスタには、次のようにラベルがふられています。

F,A,B,C,D,E,H,L,F',A',B',C',D',E',H',L',IX,IY,SSP,USP,PC,I,R。 |

| CPUコントロール&ステータスレジスタ空間 |

| CPUコントロールレジスタ空間は、CPUコントロールレジスタ中の全コントロール及びステイタスレジスタからなっています。これらのレジスタはCPUのオペレーションを管理し、特権命令であるロードコントロール命令(LDCTL)によってのみアクセスが可能です。CPUコントロールレジスタファイルには次のようなものがあります。 |

|

|

マスターステータス |

|

|

バスタイミング&イニシャリゼーション |

|

|

バスタイミング&コントロール |

|

|

インタラプト/トラップベクタテーブルポインタ |

|

|

I/Oページ |

|

|

システムスタックリミット |

|

|

トラップコントロール |

|

|

インタラプトステータス |

|

|

キャッシュコントロール |

|

|

ローカルアドレス |

|

| メモリアドレス空間 |

Z800CPUは2種類のメモリアドレス空間をサポートしています。1つはユーザモードのオペレーション用、もう1つはシステムモードでのオペレーション用です。これはマスターステータスレジスタ中の「ユーザ/システムモード(U/S)」ビットにより決定されます。このマスターステータスレジスタは、アドレス変換の間、ページディスクリプタレジスタの選択を管理します。

それぞれのアドレス空間は64KB単位のメモリブロックが番号をふられて昇順に並んでいるように見えます。8bit、つまり1バイトがメモリアドレス空間内での基本アドレッシング単位となります。この他、ビット,ワード(2バイト),バイトストリング,多バイトEPUオペランドなどがアドレッシング単位となります。

多バイトをアクセスする際のアドレスは、そのストリングデータの先頭のアドレスです。また、奇数、偶数どちらのアドレスからでもストアすることができます。 |

| I/Oアドレス空間 |

| I/Oアドレスは、I/O命令のIN,OUT及びI/Oブロック転送命令によってのみ発生します。論理I/Oアドレスは8bit長ですが、直接アドレスアドレッシングモードではAレジスタの内容が、レジスタ間接アドレッシングモードやブロックI/O命令ではBレジスタの内容がアドレスラインA8-A15上にそれぞれ出力されることで拡張されています。16bit論理I/Oアドレスは、8bitのページレジスタの内容を加えることにより、常時拡張されていると考えることができます。このように、I/Oポートを決定するために発生する最終的なアドレスは、A16-A23上のI/Oページ番号、A8-A15上のAあるいはBレジスタの内容、及びA0-A7上の8bitI/Oアドレスからなるわけです。1ワード(16bit)のストアやフェッチに2回のメモリ参照が起こる場合のあるメモリアドレス空間の参照とは異なり、I/Oアドレス空間へのストアやフェッチは常に1回のI/Oバス処理で済み、バスサイズやI/Oポートアドレスには無関係です。しかし、ワードレジスタを持つZ800チップ内の周辺デバイスは、外部バスサイズにかかわらずワードI/O命令を通してそれらの16bitレジスタがアクセスされることに注意する必要があります。 |

|

|

|

| CPUはビット,BCD(4bit),バイト(8bit),ワード(16bit),バイトストリング,ワードストリングなどのデータ型が扱えます。レジスタやメモリ中の任意のビットをセットしたり、クリアしたり、テストしたりできます。また、パック型BCDがバイナリ加減算命令(ADDやSUBなど)とDAA命令を併用することによって扱うことができます。バイトは、ロード、算術演算、論理演算、シフト、ローテイトが可能。ワードも同様に16bitロード、16bit算術演算が可能です。ブロック転送とブロックサーチ命令は、最大64KBまでのバイトストリングを扱え、ブロックI/Oワード命令は、32KWまでのワードストリングを扱えます。そしてEPUのオペレーションをサポートするために、16バイトまでのバイトストリングがCPUより転送できるようになっています。 |

|

|

|

|

コラム2 Z8000ファミリー |

Z800と同じ16bitCPUに“Z8000ファミリー”がザイログ社にはあります。というか、ザイログの16bitCPUといえば通常はこのZ8000を指します。その発表時期はZ800より早く、ザイログ社としてもこちらの方を16bitCPUの本命と位置づけています。実際にZ8000は市場にある程度出回っており、ヤマハの家庭用コンピュータ「YIS(ワイズ)」や、アーケード版レースゲーム、ナムコ社の「ポールポジション」のサブCPUとしても使用されていました(Z8002-4MHz版×2個使用)。しかし、インテル社の8086系やモトローラ社の68000系の16bitCPUに押され、一定の市場を拓くには至りませんでした。

とりあえずデータブックに記されているZ8000の特徴を取り上げてみました。 |

|

|

直交性が良く、使いやすいアーキテクチャ |

|

|

他のCPUと比べてもパワフルな命令セット |

|

|

8MBのメモリ空間 |

|

|

ユーザが自由に選択できる8種類のアドレッシングモード |

|

|

32bitのロングワードの他、バイトおよびワードのストリングデータなど7種類のデータタイプ |

|

|

システムとユーザ、2つのオペレーティングモード |

|

|

分離されたコード領域とデータ、スタック領域 |

|

|

洗練された割り込み処理構造 |

|

|

マルチプロセシングシステムのためのリソース共有能力 |

|

|

コンパイラのサポート |

|

|

8010MMUのサポート |

|

|

符号付き乗除算を含む32bitオペレーション |

|

|

Z-BUSコンパチブル |

|

|

4,6,10MHzクロック |

|

以上のようにZ80から引き継がれているのはZ-BUSくらいのものです。全く新しいCPUとして設計されていることが見て取れます。あきらかにZ800とは一線を画しており、「Z800は16bit版Z80である」という確信が持てます。 以上のようにZ80から引き継がれているのはZ-BUSくらいのものです。全く新しいCPUとして設計されていることが見て取れます。あきらかにZ800とは一線を画しており、「Z800は16bit版Z80である」という確信が持てます。

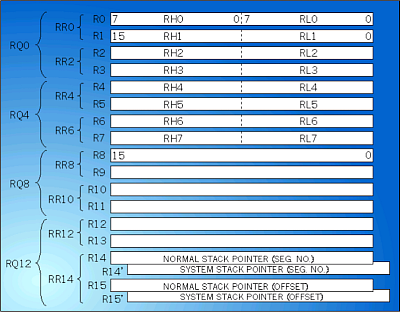

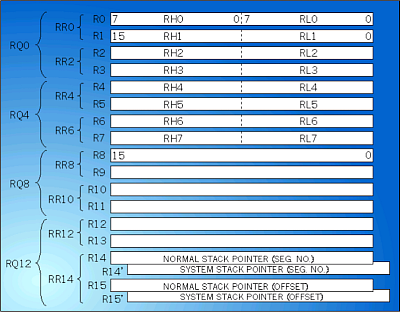

折角ですので(?)、代表的なZ8000ファミリCPUであるZ8001の汎用レジスタファイルを右に示します。もちろんこれら以外にプログラムカウンタなどのスペシャルレジスタが何本か存在します。

ご覧のように非常にすっきりとわかりやすい体系になっています。ほぼ等価な16本の16bitレジスタ、そのうち半数が上位下位8bitを独立した2本の8bitレジスタとして扱えるため、16本の等価な8bitレジスタが存在することになります。さらに、連続した番号の2本の16bitレジスタを1本の32bitレジスタ(RR0~RR14)としても扱え、これが8本。そしてまたさらに32bitレジスタ2本で64bitとして・・・・といくように見えますが、RQ0~12の4本はDIVLやMULTLといった乗除算などごく一部の命令でのみ使用されます。

Z8000はMC68000のような64ピンの大きなチップ(俗称:お化けチップ)ではなく、40または48ピンのパッケージで簡単に32bit演算を実行できたこともメリットのひとつだったようです。当時のハードウェア技術者たちが慣れていたZ-BUSだったことも無視できません。ちなみに80286も16ビットCPUで68ピンパッケージですが、32bitの演算命令はありませんでした。

比較のため32bitのレジスタ間加算命令等の消費クロック数を見てみると表のようになります。(80286は16bit演算による等価プログラムの総クロック数。)

|

|

|

|

|

|

|

|

Z8000 |

68000 |

80286 |

|

|

|

|

32bit整数加算 |

14 |

8 |

4 |

|

|

32bitゼロTEST |

14 |

4 |

2 |

|

|

32bit右3bitシフト |

22 |

14 |

12 |

|

|

|

|

|

|

|

|

|

ご覧のように Z8000のクロック効率はよくありません。もちろんこれは32bit演算の話であって、16bit演算はこれほど酷くはありませんが、それでもやはり見劣りするものです。しかし、Z8000には他を圧倒するような「使いやすさ」があります。レジスタの組み合わせや用法を工夫することで、他の16bitCPUには真似のできない(メモリアクセスの少ない)高効率なプログラムを組むことも可能です。この点はコンパイラの作成に大きく寄与する部分です。そういった意味では「高速性」よりも「効率性」を重視したCPUと言えるでしょう。残念ながらこのことは市場に広く受け入れてもらえたとは言い難く、マイナーな存在のまま終焉を迎えました。

|

|

| P.S.上の表からは32bit演算能力が弱いように見えますが、乗除算に関しては特筆すべき能力を持っています。他の16bitCPUは乗算が16bit×16bit = 32bit、除算が32bit÷16bit = 16bitというものですが、Z8000だけは32bit×32bit = 64bit、64bit÷32bit = 32bitという、真の32bit演算をサポートしています。乗算で282クロック、除算で744クロック要しますが、他CPUの等価プログラムに比べても十分に高速です。精度の高い整数演算が求められる分野にはとても魅力的に映ったはずです。 |

|

|