|

|

|

|

「64ビットCPUの時代に16ビットCPUの話?!」と驚かれる方も多いでしょう。確かにその通りです。今となっては全く忘れ去られてしまった存在であり、それについて知ることに意味があるのか疑問に思われるでしょう。ところが意外とそうでもないのです。

結果的に言うとZ800は失敗でした。Z800という名のCPUが市販されることもありませんでしたし、ザイログ社が自社の歴史から抹消したくらいです。しかし、そのアーキテクチャは当時としては目を見張るものがありました。何と言ってもZ80のオブジェクトコンパチであった点は見逃せません。一見すると類似したことをモステクノロジー社が実行し、それなりの成果を上げています。(→コラム1)NECもμPD9002というZ80互換モードを持つV30のサブセットCPUを自社のPC-88VAというパソコンに登載していました。が、両社のCPUはどちらもハードウェア・エミュレーションにより互換を実現しており、リセット時に切り替えることしかできません。命令の混在はできなかったのです。この点、Z800は混在が前提です。

しかし、Z800が興味深いのは決してこれだけではありません。MMU(メモリー管理ユニット)やDMA(ダイレクトメモリーアクセス)機能、タイマ/カウンタ、UART(シリアル通信インタフェース)を内蔵していたりします。このあたりは日立のHD64180(Z80コンパチ+周辺LSI)にとても似ています。(余談ですがHD64180はザイログ社自らがセカンドソースとなり、Z180という名称で製造販売していました。)ところがZ800には、さらに「高速キャッシュメモリ」が内蔵されており、Z80として使用した場合も、かなりの高性能が見込めます。 |

さて、Z800は1983年にザイログ(Zilog)社が発表した16ビットCPUです。ただ、ザイログ社では“Z800 CPU”ではなく、“Z800 MPU”と呼んでいます。MPUというとモトローラ社の呼び名と同じですが、ザイログ社ではCPUにある程度の周辺機能を組み込んだものを“MPU”と呼ぶようです。ですから、Z80・Z8000・Z80,000は“CPU”、Z8は“MCU (MicroComputerUnitの略?)”と呼んでいます。本記事では便宜上“Z800 CPU”と呼ぶことにします。

これからの話の中にもZ80はもとよりZ8000やZ80,000などの引用が出てくると思いますが、こちらはコラムで紹介いたしますので、そちらを参照してください。(→コラム2,コラム3)

また、Z800の仕様に関する情報は「’84年版ザイログ社データ・ブック」によるものです。Z800は後に“Z280”という名称で若干の仕様変更を経ていちおうの日の目を見ますが、量産されることなくすぐに消えていきます。ここでご紹介する情報はあくまでも1984年当時の情報であることをあらかじめご理解ください。

|

|

コラム1 モステクノロジーのCPU

|

モステクノロジー社といえばApple][(あっぷる・つー)のCPUであった8ビットの6502で有名です。また、そのサブセット版は任天堂のファミコンにも採用されています(リコー社製RP2A03という名称のカスタムチップ)。さらにメモリー管理機能を強化した6510はNECのPCエンジンに採用されています(Hu6280という名称で6510のメモリアクセスエリアを拡大し[確か1MBまで]、ブロック転送命令を追加し、さらに動作クロックを引き上げたもの)。

このモステクノロジーが発表した65808/16という16ビットCPUは6502のオブジェクトコンパチモードを持ち、65816は任天堂のスーパーファミコンやApple][GSに採用されました。しかしこれは実際にはエミュレートモードに切り替えて8ビットコンパチを実現していました。ところがZ800ではネイティブに実現します。つまり、モードの切り替えが不要で、8ピットコードと16ビットコードが完全に混在できることを意味しています。これはインテルの32ビットCPU80386が、35ビットモードでも8086の16ビット命令をすべて実行できるのに似ています(Pentium4になっても可能なままです)。

|

|

|

|

|

|

| Z800は次のような特徴を持っています。 |

|

|

Z80マイクロプロセッサとオブジェクトコードレベルでコンパチビリティーを維持しながらも、さらに強化されたインストラクション・セット |

|

|

ページMMU内蔵 |

|

|

広大なメモリアドレス空間。512KBと16MBバージョン |

|

|

高速ローカル・メモリ/キャッシュ・メモリ搭載 |

|

|

高パフォーマンス16bit Z-BUSインタフェース、及び 8bit Z-80コンパチのバス・インタフェース装備 |

|

|

4つの16bitカウンタ/タイマー内蔵 |

|

|

4つのDMAチャネル内蔵 |

|

|

全二重UART内蔵 |

|

|

10~25MHzのCPUクロック |

|

| 8/16bitマイクロプロセッサであるザイログ社の「Z800ファミリー」は、当時のエンドユーザーのために高性能・低価格を実現すべく設計されたハイ・パフォーマンスなマイクロプロセッサです。このファミリーは40/64ピンのデュアルインラインパッケージに納められた8bitのZ80-BUSマイクロプロセッサと、同様に40/64ピンの16bit Z-BUSマイクロプロセッサよりなります。Z800ファミリーは高速化、より効率的なスループット、Z80とオブジェクトコンパチを維持しながらのメモリ空間の増加など、先進の設計技術を取り入れています。Z800マイクロプロセッサは、Z80を基礎とした構想を踏襲しながら、新しい構想を目指したハイパフォーマンス・マイクロプロセッサとして企画されました。 |

| Z800はZ80CPUの強化バージョンであるということができます。システムを保護するため、システムモードとユーザーモードのどちらの状態であっても、ユーザーのタスクやプログラムからシステム資源の保護に関する操作が可能です。システムモードのオペレーションは、ワーキングレジスタセットへの機能付加によりサポートされます。IX,IYレジスタはインデックスレジスタとしての機能に加えて、16bitの汎用レジスタ、あるいは2本の8bitレジスタとしてもアクセスできるようになっています。これはZ80でも可能でしたが、「隠れ命令」として存在いましたから、これが正式にサポートされたということになります。 |

Z80の命令セットはすべてそのまま保持されています。これはZ800がZ80のコードと完全にバイナリコードコンパチであることを意味しています。Z80の基本的なアドレッシングモードに加えて、プログラムカウンタ(PC)相対やスタックポインタ(SP)相対、及びベースインデックスモードなどの完全16bitディスプレースメントインデックスモードが追加されています。新たなアドレッシングモードは旧Z80CPUの数ある命令にさらに追加された形になっており、命令セットはより柔軟に、かつ強力になっているといえます。他にも8,16bitの符号付き/符号無し乗除算,8,16bit符号拡張,マルチプロセッシングをサポートするためのtest, set命令などがあります。また、16bitのコンペア,メモリインクリメント,メモリデクリメント,符号反転,加算,減算命令などを追加するために16bit命令が拡張されています。これは以前にザイログ社が発表していた乗算及び除算命令にさらに新しく追加された機能です。 Z80の命令セットはすべてそのまま保持されています。これはZ800がZ80のコードと完全にバイナリコードコンパチであることを意味しています。Z80の基本的なアドレッシングモードに加えて、プログラムカウンタ(PC)相対やスタックポインタ(SP)相対、及びベースインデックスモードなどの完全16bitディスプレースメントインデックスモードが追加されています。新たなアドレッシングモードは旧Z80CPUの数ある命令にさらに追加された形になっており、命令セットはより柔軟に、かつ強力になっているといえます。他にも8,16bitの符号付き/符号無し乗除算,8,16bit符号拡張,マルチプロセッシングをサポートするためのtest, set命令などがあります。また、16bitのコンペア,メモリインクリメント,メモリデクリメント,符号反転,加算,減算命令などを追加するために16bit命令が拡張されています。これは以前にザイログ社が発表していた乗算及び除算命令にさらに新しく追加された機能です。 |

| 通常の8bitマイクロプロセッサベースのシステムデザインにおいてよく聞かれる要望は、64KB超のアドレス空間をサポートすることです。Z800は、アドレス空間を512KB、あるいは16MBに拡張するオンチップMMUを搭載しています。また、アドレス空間の拡張に加えて、このMMUは他の外部メモリマネジメントデバイスを制御するメモリ管理機能をあらかじめ持っています。 |

| I/Oアドレス空間は、“I/Oページレジスタ”の追加によって拡張されています。8bitのI/Oページレジスタが、256ページあるI/Oアドレスページの中からアクティブになる任意の1ページを決定する仕組みになっています。これによって、アクセス可能なI/O空間はトータルで64KBになります。(256×256 = 64KB) この64KBのI/Oアドレス空間もZ80の「隠れ機能」として有名でしたが、このような形態で正式サポートされています。 |

| また、すべてのZ800ファミリーには256バイトのメモリが内蔵されています。このメモリは高速キャッシュとしても、また固定アドレスのローカルメモリとしても扱うことができます。まず、これをキャッシュとして扱った場合、命令のみ、データのみ、あるいは命令&データにするか任意に設定できます。キャッシュを利用すれば、外部バス経由のメモリーをアクセスするよりも高速ですから、当然プログラムも高速に走らせることができるようになります。キャッシュの操作及び更新は自動的に行われ、ユーザに対して完全に透明です。次に、ローカルメモリとして使用した場合、そのアドレスはプログラマブルになっています。これは“RAM-less”システムに応用できそうです。つまり、組み込み用途にも大変有効と思われます。 |

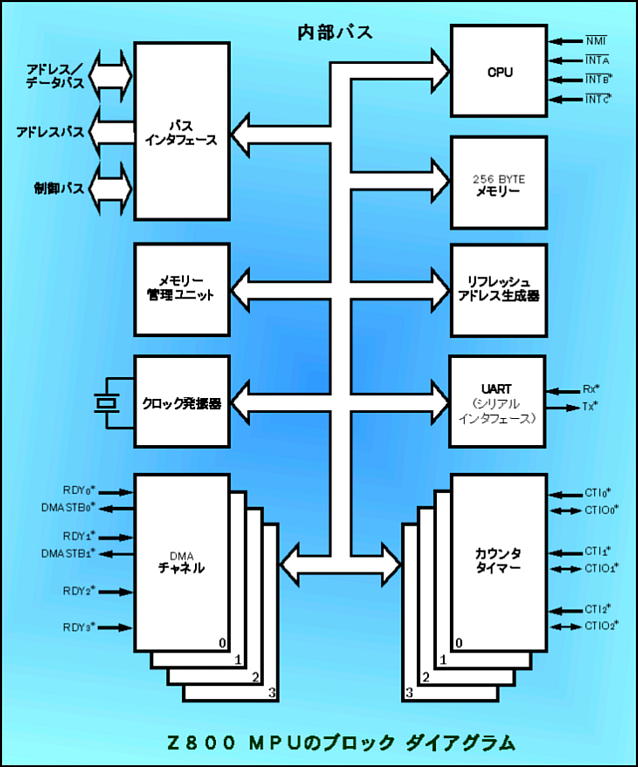

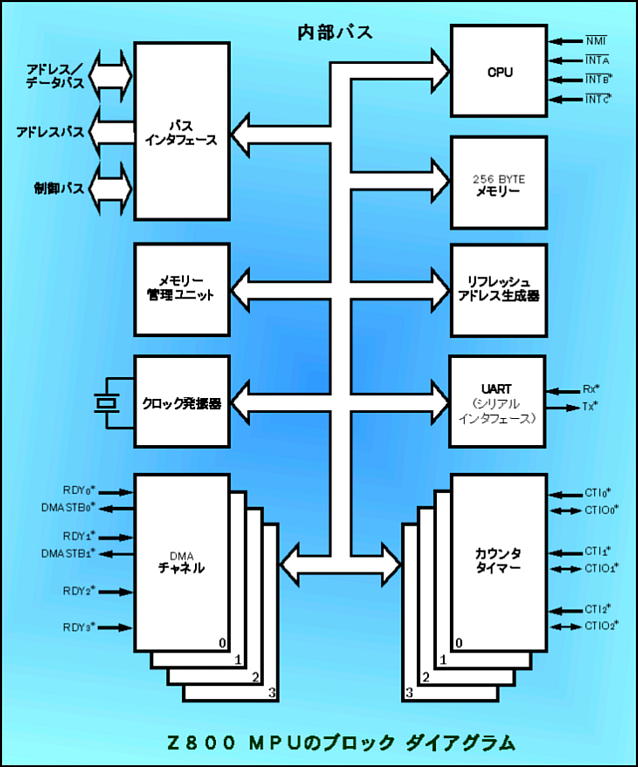

| 外部周辺デバイスによって伝統的に培われてきた数々の特徴は、Z800の設計にも受け継がれています。周辺デバイスをオンチップ搭載することでシステムのチップ総数を減らし、外部バス上の各チップ間の相互関係を減少させる働きがあります。また、Z800ファミリーはすべてクロックジェネレータをチップ内に持っていて、ダイナミックRAM使用時のために、10bitのリフレッシュアドレスを出力するリフレッシュコントローラも装備しています。 |

| Z800の64pinバージョンは、システム設計に柔軟性を持たせるために、チップ内に定番の周辺デバイスを持っています。例えば、広範囲に渡るデータ転送をサポートするための4つのダイレクト・メモリ・アクセス(DMA)チャネル。各DMAチャネルは24bitで指定される転送元と転送先アドレス、そして16bitのカウンタで制御されます。チャネルは、シングル、バースト、またはコンティニュアスの各モードで動作するようにプログラム可能です。システムイベントのカウントやタイミング要求は、4つの16bitカウンタ/タイマによってかなえられます。このカウンタ/タイマの機能は、外部からのゲート入力及びトリガ入力によって制御され、リトリガラブルかノンリトリガラブルか指定することができます。また、さまざまなデータ/キャラクタフォーマットに対処できる全二重UARTが非同期シリアル通信をサポートしています。 |

| Z800ファミリーは、8bitバスでも16bitバスでも使用できるように、バスタイミングがプログラムできるようになっています。これによって、ユーザが独自のシステムにも自由にタイミングを合わせることができるようになります。リセット状態においてZ800は、CPUのスピードに応じて1:4,1:2,1:1の中から選んでシステムタイミングをプログラムすることができます。ディフォルト値は1:2になります。クロックのスケーリングに加えて、プログラム可能なウエイトステートをいろいろなバス処理間に挿入することもできます。さらに、別々のメモリウエイトステートを、メモリの上限アドレスと下限アドレスの設定によって細かく指定できます。同一システムにおいて、速度の異なるROMやRAMが混在しているときにとても重宝します。16bitバスインタフェースに付加された機能は、ニブルモードを持つダイナミックRAMのサポートです。(バーストモードとして知られている)この機能を利用すると、メモリREAD処理のバス帯域が本質的に二重化されます。バーストモードには、ヒット率(アクセスされたメモリの内容がキャッシュ内にある確率)を高めることにより、より効率的にキャッシュが機能するという利点もあります。(事実、このキャッシュを内蔵したZ280は、キャッシュを切るとお世辞にも高速とはいえませんでしたが、オンにするといきなり何倍も高速化するそうです。今の感覚だとたかだか256バイトですが、8bitのコードを考えると主たるプログラムのループはほとんど収まってしまいそうですので、キャッシュのモード設定やメインメモリのレイテンシー、回路設計も関与しますが、あながちウソではなさそうです。) |

| Z800ファミリーは様々な手段でザイログ社の拡張プロセッサアーキテクチャ(EPA)をサポートしています。これらはみな、拡張プロセッサユニット(EPU)のソフトウェアエミュレーションを実行するために、EPUに関する命令(RETI:ED 4D)をトラップできるようになっています。Z8216は、Z8070浮動小数点演算ユニット(FPU)のようなEPUと直接接続できます。この他のZ800ファミリーも、ソフトウェアの力を借りることによって容易にEPUとインタフェースできます。 |

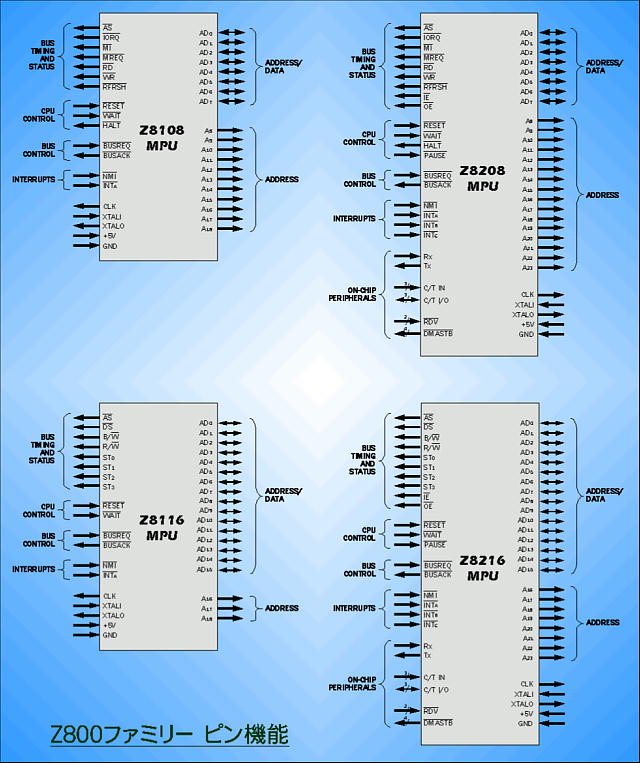

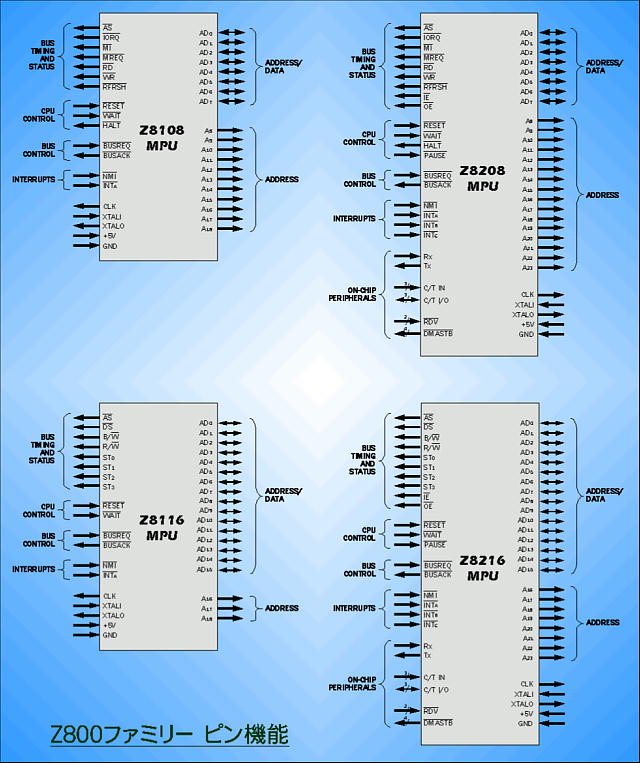

| Z800CPUの4つのバージョンのピン配置とブロックダイアグラムを以下に示します。 |

|

|

|

※上図の各チップをクリックすると拡大図が表示されます

|

|

|

Z80の命令セットはすべてそのまま保持されています。これはZ800がZ80のコードと完全にバイナリコードコンパチであることを意味しています。Z80の基本的なアドレッシングモードに加えて、プログラムカウンタ(PC)相対やスタックポインタ(SP)相対、及びベースインデックスモードなどの完全16bitディスプレースメントインデックスモードが追加されています。新たなアドレッシングモードは旧Z80CPUの数ある命令にさらに追加された形になっており、命令セットはより柔軟に、かつ強力になっているといえます。他にも8,16bitの符号付き/符号無し乗除算,8,16bit符号拡張,マルチプロセッシングをサポートするためのtest, set命令などがあります。また、16bitのコンペア,メモリインクリメント,メモリデクリメント,符号反転,加算,減算命令などを追加するために16bit命令が拡張されています。これは以前にザイログ社が発表していた乗算及び除算命令にさらに新しく追加された機能です。

Z80の命令セットはすべてそのまま保持されています。これはZ800がZ80のコードと完全にバイナリコードコンパチであることを意味しています。Z80の基本的なアドレッシングモードに加えて、プログラムカウンタ(PC)相対やスタックポインタ(SP)相対、及びベースインデックスモードなどの完全16bitディスプレースメントインデックスモードが追加されています。新たなアドレッシングモードは旧Z80CPUの数ある命令にさらに追加された形になっており、命令セットはより柔軟に、かつ強力になっているといえます。他にも8,16bitの符号付き/符号無し乗除算,8,16bit符号拡張,マルチプロセッシングをサポートするためのtest, set命令などがあります。また、16bitのコンペア,メモリインクリメント,メモリデクリメント,符号反転,加算,減算命令などを追加するために16bit命令が拡張されています。これは以前にザイログ社が発表していた乗算及び除算命令にさらに新しく追加された機能です。