|

|

|

|

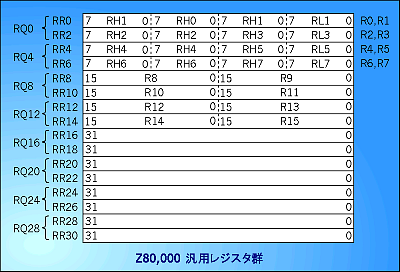

| Z800MPUは、CPUレジスタ空間に23本のプログラマブルレジスタを持っています。(下図) 驚くべきというか、残念というか、Z80と全くといってよいほど変わっていません。スタックポインタが1本増えただけです。16bitCPUとしては実質的に汎用レジスタを5本しか持っていないことになります。うち3本はバンクが存在するため、5+3=8本と言えなくもないですが、やはり新たに16bit汎用レジスタを追加してもらいたかったものです(例えばGレジスタとJレジスタとか・・・)。 |

|

|

| プライマリー&ワーキングレジスタ群 |

ワーキングレジスタセットは2つの8bitレジスタファイルに分けられています(表レジスタファイルと裏レジスタファイル)。各レジスタファイルは、アキュムレータ(A)とフラグレジスタ(F)と6本の汎用レジスタ(B,C,D,E,H,L)からなっています。これらのレジスタファイルは、一時には一方のレジスタファイルだけがアクティブになります。つまり、同時にはアクティブになりません。リセット時は表がアクティブになります。プログラマはエクスチェンジ命令(EX,EXX)によって、アクティブファイルとイナクティブファイルを随時自由に交換できます。

アキュムレータは8bit算術及び論理演算命令におけるディスティネーションレジスタです。6本の汎用レジスタはペアになって3本の16bit汎用レジスタになります。BC,DE,HL、中でもHLレジスタペアは16bitの算術演算命令において16bitアキュムレータとして働きます。 |

|

|

| CPUフラグレジスタ |

| フラグレジスタは各種CPUのオペレーションによりセット/リセットされる6個のフラグからなります。 |

|

|

| キャリー(C) このフラグは加算命令で桁上がりが生じるか、減算命令で桁借りが生じるとセットされます。特定の論理演算やローテイト、シフト命令もこのキャリーフラグに影響を与えます。 |

| 加算/減算(N) このフラグは加算と減算を区別するためにDAA命令で使用されます。加算でセットされ、減算でクリアされます。 |

| パリティー/オーバーフロー(P/V) このフラグは実行される命令によって、セット/クリアされます。算術演算時はオーバーフローを示し、論理演算やローテイトなどでは結果が偶数であればセットされ、奇数であればクリアされます。 |

| ハーフキャリー(H) このフラグは8bitの算術演算命令で、bit3とbit4の間にキャリーまたはボローが生じたとき、あるいは16bitの命令でbit11とbit12の間に桁上がり、または桁借りが生じたときにセットされます。このビットは、パック型BCDの加算および減算命令を実行した結果を補正するために使用されるものです。 |

| ゼロ(Z) このフラグは算術演算または論理演算の結果が0のときセットされます。 |

| サイン(S) このフラグはアキュムレータのMSB(bit7)の状態が格納されます。このフラグはtestやset命令の結果を示すためにも使用されます。 |

| 以上、早い話がZ80と全く同じです。 |

|

|

| 専用CPUレジスタ |

| インデックス・レジスタ |

| 2本のインデックスレジスタIX,IYは、インデックスアドレッシングモードで使用される16bitベースアドレスを保持するためのものです。インデックスレジスタは上位下位独立してアクセスできる汎用レジスタとしても使えます。IXレジスタの上位バイト及び下位バイトは、それぞれIXH,IXLと呼び、同様にIYレジスタの場合は、IYH,IYLと呼びます。Z80でも未定義命令(隠し命令と言った方が一般的かも)としてバイトアクセスが可能でしたが、これが正式サポートされました。 |

| インタラプト・レジスタ |

インタラプトレジスタ(I)は、割り込みサービスルーチンへのジャンプアドレスを指す16bitの間接論理アドレスを生成するために、モード2割り込みで使用されます。インタラプトレジスタはこの間接アドレスの上位8bitを保持しており、下位8bitは割り込み発生源の周辺デバイスが与えることになっている。

Z80をご存じの方ならば解説不要でしょう。Z80の大きな特徴でもあるモード2割り込みを使用すれば、プログラマは割り込みソースを毎回割り込みサービスルーチンでチェックする必要がなく、大変効率よく割り込み処理を記述できました。このインタラプトレジスタに割り込みベクタテーブルの先頭アドレスの上位8bitを設定しておけば、割り込みを発生させたモード2割り込み対応の周辺LSI(Z80-CTC,SIO,PIO,DMA,DARTなど)にベクタオフセットをあらかじめ設定しておくだけ(Interrupt Vector Wordレジスタ)で、割り込み発生時には自動的に適切な割り込み処理ルーチンへジャンプしてくれるというわけです。

ちなみにモード2割り込みを全く使用しない(できない)システムでは、このIレジスタは8bitのテンポラリレジスタとしても使用できます。 |

| プログラム・カウンタ |

| プログラムカウンタ(PC)は、現在実行中のプログラムの命令のアドレスを指したり、相対アドレスの生成に使用されます。このレジスタはメモリからフェッチされた現在の命令の16bit論理アドレスを示しています。 |

| Rレジスタ |

| Rレジスタは、8bitのリード/ライト可能な汎用レジスタとして使用できます。Z800では、このレジスタはリフレッシュアドレスとは全く関連がなく、その内容はユーザによってのみ変更されます。Z80で疑似乱数の生成などにこれを利用していたプログラムは正常に動作しなくなるわけです。注意すべき変更点のひとつでしょう。 |

| スタック・ポインタ |

| ユーザスタックポインタ(USP)とシステムスタックポインタ(SSP)は、マイクロプロセッサの2種類の動作モードをサポートするものです。SSPは、割り込みやトラップが発生したときの情報を退避したり、システムモードにおけるサブルーチンのコールやリターンをサポートするための使用を前提にしています。 |

|

|

| ステータス&コントロール・レジスタ |

| Z800MPU内部には、プログラマが利用可能な10本のステータス&コントロールレジスタがあります。次の表はステータス&コントロールレジスタ空間内のアドレスマップです。 |

|

|

|

アドレス(HEX) |

|

コントロールレジスタ名 |

|

|

|

Control 00 |

|

Master Status(MSR) |

|

Control 02 |

|

Bus Timing and Control |

|

Control 04 |

|

Stack Limit |

|

Control 06 |

|

Interrupt/Trap Vector Table |

|

Control 08 |

|

I/O Page Register |

|

Control 10 |

|

Trap Control |

|

Control 12 |

|

Cache control |

|

Control 14 |

|

Local Address Register |

|

Control 16 |

|

Interrupt Status |

|

|

|

|

|

Control FF |

|

Bus Timing & Initialization |

|

|

|

|

| バスタイミング&コントロールレジスタ |

| この8bitのレジスタは、高メモリアドレス(MMUによって制御されるアドレス)処理や割り込み要求に対してのデイジー・チェインのタイミングを管理します。つまり、Z800MPUの割り込み要求ライン上のそれぞれのテバイスの特性に合わせて値が決定されることになります。リセット時には全ビットが0にクリアされます。 |

|

|

| このレジスタのフィールドは以下の通りです。 |

| I/Oウエイト挿入(I/O) この2bitフィールドは、I/O処理やベクタのレスポンス・タイミングに挿入される追加ウエイト・ステート(I/O処理時に自動的に挿入される1ウエイトに加えてさらに挿入される)数を表しています。(00=無し、01=1、10=2、11=3) |

| ハイメモリウエイト挿入(HM) この2bitのフィールドは、MMUがイネーブルで、かつ選択されたページ・ディスクリプタ・レジスタのbit15が“1”の期間中、メモリ処理時に自動的に挿入されるウエイトステート数を表します。(00=無し、01=1、10=2、11=3) |

| ディジー・チェインタイミング(DC) この2bitフィールドはディジー・チェインの割り込み応答中に自動的に挿入されるウエイトステート数を指定します。(00=無し、01=1、10=2、11=3) つまり、DCフィールドの値が“01”のときは、通常の4サイクルに1サイクルが追加されて(4+1=5)、割り込み応答ASとDS信号の間に挿入されることを示します。 |

|

| バスタイミング&初期化レジスタ |

この8bitレジスタは、MMUがディゼーブル状態のときか、あるいはイネーブル状態でかつ選択されたページ・ディスクリプタ・レジスタのbit15が“0”のときに、外部バス制御信号の持続時間を指定のに使用されます。また、プロセッサ内部のクロックレートとバスタイミングの関係もコントロールしています。このレジスタは、リセット時に外部ハードウェアによって初期設定できるようになっています。

リセット時、このレジスタは2通りある設定のうちのどちらか1つで初期化されます。この選択は、リセット信号の立ち上がり時のWAIT入力の状態により決定されます。アサートでなければレジスタには'00'Hがセットされ、アサートだとその時点でのデータバスの値がセットされます。 |

|

|

| このレジスタのフィールドは次の通りです。 |

| クロックスケーリング(CS) この2bitのフィールドには、全バス処理のCPUクロックのスケーリングを設定します。(00=1バスクロックサイクルはプロセッサ内部2クロックサイクルに等しい。01=バスクロックサイクルはプロセッサ内部クロックサイクルに等しい。10=1バスクロックサイクルはプロセッサ内部4クロックサイクルに等しい。11=リザーブ。) このフィールドはソフトウェアでは操作できません。先の説明にあるように、リセット時に外部ハードウェアで設定します。 |

| ローメモリウエイト挿入(LM) この2bitフィールドは、MMUがディスエーブルのときか、あるいはMMUがイネーブルでかつ選択されたページ・ディスクリプタ・レジスタのbit15が“0”のとき、メモリ処理時に自動的に挿入されるウエイトステート数を表します。(00=無し、01=1、10=2、11=3) |

| マルチプロセッサ形成イネーブル(MP) この1bitフィールドはマルチプロセッサモードの指定を行うものです。(0=不可、1=可)〔マルチプロセッサモードの章参照〕 |

| ブートストラップモードイネーブル(BS) この1bitフィールドはブートストラップモードの指定を行うものです。(0=不可、1=可)〔ブートストラップモードの詳細についてはUARTの章参照〕 |

|

|

|

|

|

コラム3 Z80,000 CPU |

知名度としてはZ800とZ8000の中間くらいでしょうか。Z8000がザイログ社の真の16bitCPUとするならば、Z80,000は真の32bitCPUであるといえるでしょう。32bit長の汎用レジスタが16本あり、4GBのフラットなメモリ空間を持っていて、32本のデータバス(アドレスバス32本とマルチプレクス)がチップから出ていました。発表当時は各社から32bitCPUのアナウンスがあり、インテルの80386、モトローラの68020、ナショセミの32032、NECのV70などと共にザイログのZ80,000も話題になっていました。さらにはRISCブーム(?)が起こり、PowerPC、MIPS3000シリーズ、SPARCシリーズ、SH-3など、多様な32bitCPUのシェア合戦が繰り広げられました。結果的には皆様ご存じのとおり、ほとんどインテルの一人勝ち状態となりました('05現在はAMDが64bitCPUで健闘中)。

ところがZ80,000はZ800の二の轍を踏みます。市場投入が遅れ、ほとんど日の目を見ませんでした。ザイログも必死に開発をしていたのですが、Z80,000は放熱でのたうち回ったようです。Z80以来のN-MOSデバイスでチップを作ろうとしたことに無理があったのです。当時で数十ワットの消費電力ということでしたらから、かなり大型の放熱器と電源が必要だったようです。そうこうしているうちに時は流れ、結局C-MOSデバイスで発売したときには「時すでに遅し」でした。ちなみに発売されたときの型番はZ80,000ではなく、“Z320”というものでした。これもなんとなくZ800のパターンと似ています。パイプライン構造を持ち、キャッシュメモリやMMUを内蔵していたり、80386の仮想86モードのようにZ8000のバイナリ互換だったりと、先進の機能満載だったのですが・・・・。余談ですが、手元のマニュアルでは58本の信号線を持つことになっているので、製品は68pin程度のフラットパッケージかお化けチップになっているものと思われます(未確認)。

ここで話が終わってしまうと寂しいので、こちらもコラム2のZ8000のように、特徴とレジスタ構成を見てみましょう。 |

|

|

完全な32ビットアーキテクチャとインプリメンテーション |

|

|

4ギガバイト(約42億バイト)の直接アドレス可能なメモリ空間 |

|

|

リニア、あるいはセグメント化されたアドレス空間 |

|

|

仮想メモリ管理ユニット(MMU)をCPUに内蔵(ページングサポート) |

|

|

キャッシュメモリ内蔵 |

|

|

16本の汎用32bitレジスタ群 |

|

|

9種類のアドレッシングモード |

|

|

豊富なデータ型(ビット、ビットフィールド、論理値、符号付き整数、およびストリングなど) |

|

|

メインフレームパフォーマンス |

|

|

拡張アーキテクチャにより浮動小数点演算をサポート |

|

|

直交性の良い命令体系 |

|

|

2本のスタックポインタによるシステムモードとユーザモードのサポート |

|

|

洗練された割り込みとトラップ処理 |

|

|

Z8000(TM)ソフトウェアとバイナリ互換 |

|

|

ハードウェアは他のZ-BUS(TM)コンポーネント互換 |

|

32bitCPUとして十分な機能を持ち合わせているのがわかります。汎用レジスタ群も実に整然としていて、直交性の高さを伺わせます。RR0~RR14の8本の32bitレジスタはZ8000CPUのものそのものである点も見逃せません。Z8000がすでにこのZ80,000を睨んで設計されていたことが推察されます。 32bitCPUとして十分な機能を持ち合わせているのがわかります。汎用レジスタ群も実に整然としていて、直交性の高さを伺わせます。RR0~RR14の8本の32bitレジスタはZ8000CPUのものそのものである点も見逃せません。Z8000がすでにこのZ80,000を睨んで設計されていたことが推察されます。

最後は9種類あると謳っているアドレッシングモードについて紹介しましょう。レジスタ直接・イミディエイト(直値)・レジスタ間接・アドレス直接・ベース+インデックス、ベース+ディスプレースメント、これら6種類はごく一般的なもので、特に語ることはないでしょう。また、ベース+インデックス+ディスプレースメントも32bitCPUとしては当然の機能といえます。特徴的なのは「PC相対」と「インデックス付きPC相対」です。8bitCPUの6809がこれを持っていて当時話題になっていた機能で、「現在のプログラムカウンタからの相対アドレッシング」のことです。これを利用すると簡単にリロケータブル(ポジション・インディペンデント)な実行プログラムを作成できます。通常はOSが実行ファイルをメモリ上にロードする際にアドレスの変換作業を行いますが、この作業が不要なプログラムファイルを作成できるわけです。「PC相対」はZ8000にもありましたが、Z80,000はこれに加えてインデックスを加算できるようになったのです。OSのコンポーネントを作成する際などに威力を発揮しそうです。(V70のアドレッシングモードの豊富さに比べればカワイイものかもしれませんが・・・) |

|