|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

| 特徴 | ||||||||||||||||||||||||

|

||||||||||||||||||||||||

| Z800CPUは256バイトのオンチップメモリを持っています。このメモリは、システムあるいはユーザが自由にアドレスを設定可能なメモリにもなれば、命令またはデータのキャッシュにもなります。その使用モード(メモリとするかキャッシュとするか)は任意に指定可能です。ちなみに、リセット時には自動的に命令キャッシュとして働きます。 | ||||||||||||||||||||||||

| オンチップメモリアーキテクチャ | ||||||||||||||||||||||||

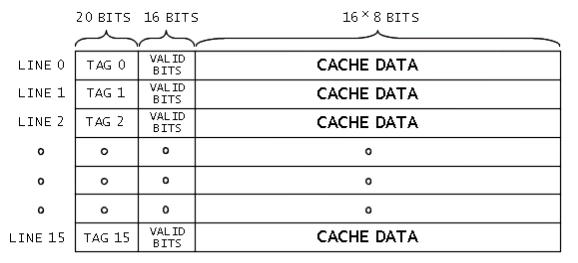

| オンチップメモリは各16バイトの16本のラインとして編成されています。各ラインは、物理アドレスである20本のMSB(=TAG n)が指す物理メモリ位置の連続した16バイトのコピーを保持します。キャッシュ内の各バイトには、連想される物理アドレスのメモリ内容の有効なコピーが、キャッシュに保持されるか否かを示す連想Validビットがあります。下図はキャッシュの構成を図式化したものです。 | ||||||||||||||||||||||||

キャッシュ構造図 |

||||||||||||||||||||||||

| オンチップメモリには2種類の動作モードがあります。キャッシュコントロールレジスタ内の「メモリ/キャッシュビット」が1にセットされると、オンチップメモリの256バイトは物理メモリとして機能します。外部バスに対してバストランザクションを発生させないオンチップメモリへのアクセスはより高速です。このモードではValidビットは無視されます。 | ||||||||||||||||||||||||

| 「メモリ/キャッシュビット」が0でクリアされると、オンチップメモリの256バイトはキャッシュメモリとして機能します。キャッシュラインはLRU(Least-Recently Used)アルゴリズムによって割り当てられます。リード時に「キャッシュミス」が発生した場合(なおかつ、MMUがキャッシュ抑制しようとしていない場合)、最近アクセスされたキャッシュのラインが、新しいリードデータを保持するために選択されます。選択されたライン内のすべてのバイトが、新しいアクセスデータを含んでいるバイトを除いて無効とマークされます。キャッシュミスが発生すると、バスサイズによって1バイトまたは2バイトが、メインメモリからフェッチされます。バーストモード命令を除けば、キャッシュは現在要求されているアドレスの他はプリフェッチをしません。データ書き込み時のキャッシュミスは、アクセスされたメモリアドレスに割り当てられてたラインは原因になりません。 | ||||||||||||||||||||||||

| このキャッシュは命令とデータの両方を保持することができます。キャッシュコントロールレジスタ内の2本の制御ビットは、命令保持用とデータ保持用とにキャッシュを別々に設定することができます。データキャッシュになっている場合、キャッシュ内のメモリアドレスに書き込みを行います。そのメモリアドレスは占有メモリアドレスを更新するための外部バストランザクションに起因します。 | ||||||||||||||||||||||||

| CPUとオンチップDMAの両方がキャッシュにアクセスすることができます。MMUが有効になっていると、CPUのメモリアクセスはキャッシュ可能にも不可能にも設定することができ、それは論理アドレスを変換するために使われるページディスクリプタレジスタ内のキャッシュ可能ビットの値によります。MMUが無効になっている場合は、全てのメモリ処理がキャッシュ可能とみなされます。キャッシュコントロールレジスタ内の2本のビット、命令キャッシュ無効ビット(I)とデータキャッシュ無効ビット(D)は、さらにさまざまなシチュエーションのキャッシュ操作を決定します。これらのビットは命令のためにもデータのためにもキャッシュを有効にします。 | ||||||||||||||||||||||||

| オンチップメモリがアドレス固定のメモリとして使用されている場合は、命令キャッシュ無効ビットもデータキャッシュ無効ビットも使用されず、CPUがデータをアクセスしていようが、命令をアクセスしていようが、全く関係なくなります。 | ||||||||||||||||||||||||

| 一般には、オンチップDMAのようなデバイスがメモリにデータを転送するとき、LRUメカニズムが影響を受けないキャッシュ内の有効なメモリアドレスへの書き込みがあるとすると、そのキャッシュデータは書き替えられることになります。また、メモリ転送EPUにおいて、キャッシュにEPUトランザクションによって更新される有効なアドレスがあるとすると、オンチップキャッシュもまた更新されます。 | ||||||||||||||||||||||||

| キャッシュコロントロールレジスタ | ||||||||||||||||||||||||

| オンチップメモリの操作は8ビットのキャッシュコントロールレジスタによってコントロールされます。このレジスタにはLOADコントロール命令を使ってアクセスします。このレジスタには5つの制御ビットがあり、それ以外のすべてのビットは0でクリアされていなければなりません。 | ||||||||||||||||||||||||

|

||||||||||||||||||||||||

| このレジスタのビットは以下の通りです。 | ||||||||||||||||||||||||

| ハイメモリバースト能力(HMB) この1ビットのフィールドは、MMUが有効で、なおかつ選択されたページディスクリプタレジスタのビット15が1のとき(0=バーストモード非サポート、1=バーストモードサポート)、メモリーバーストトランザクションが発生するかどうかを示しています。 | ||||||||||||||||||||||||

| ローメモリバースト能力(LMB) この1ビットのフィールドは、MMUが無効か、または、MMUが有効で選択されたページディスクリプタレジスタのビット15が0のとき(0=バーストモード非サポート、1=バーストモードサポート)、メモリーバーストトランザクションが発生するかどうかを示しています。 | ||||||||||||||||||||||||

| データキャッシュ無効(D) このビットが0クリアされている間は、M/Cビットが0(キャッシュモード)ならばデータフェッチがキャッシュ内にコピーされます。M/Cビットが1になっている場合は、このビットの状態は無視されます。 | ||||||||||||||||||||||||

| 命令キャッシュ無効(I) このビットが0クリアされている間は、M/Cビットが0(キャッシュモード)ならば命令フェッチがキャッシュ内にコピーされます。M/Cビットが1になっている場合は、このビットの状態は無視されます。 | ||||||||||||||||||||||||

| メモリー/キャッシュ(M/C) このビットが1にセットされている間はオンチップメモリが物理メモリとしてアクセスされ、0クリアされている間はキャッシュとしてアクセスされます。 | ||||||||||||||||||||||||

| オンチップメモリがアドレス固定のメモリとして使用される場合、ユーザは自由にメモリのアドレス範囲を選択することができます。 | ||||||||||||||||||||||||

|

||||||||||||||||||||||||

| Z800MPUには、水晶発振子またはその他いろいろなクロック発振源と接続が可能なクロックオシレータ/ジェネレータが内蔵されています。オンチップオシレータから生成されるバスタイミングクロックは、システムの負荷を減らすために出力されます。プロセッサクロックの周波数は、水晶発振子の基本周波数の1/2です。 | ||||||||||||||||||||||||

|

|

|

page

|

||||||