|

|

|

|

| 特徴 |

|

|

オンチップ・ダイナミックアドレス変換 |

|

|

広範囲な物理メモリのアドレッシングが可能 |

|

|

|

512KB - 40pinパッケージ製品 |

|

|

|

16MB - 64pinパッケージ製品 |

|

|

ユーザおよびシステムモード、それぞれ個別に用意された変換器 |

|

|

分離されたメモリエリアに存する命令コードとデータ |

|

|

個々のメモリページごとの書き込み保護 |

|

|

仮想記憶をサポートするため、アクセス違反時にはCPUがアボート |

|

|

|

| 概要 |

| Z800マイクロプロセッサーは、オンチップでメモリ管理装置(MMU)を持っていて、論理アドレスを物理アドレスに変換します。これは64Kバイト以上の物理メモリへのアクセスを可能にし、大型システムなみのメモリー保護機能を提供します。MMUによって、CPUは最高16Mバイトの物理メモリにアクセスできます。これはパッケージサイズに依存します(40ピンパッケージデバイスはアドレスを19ビットだけ出力します)。MMUは、エラー条件によってページフォルトを生成するといった洗練されたトラップメカニズムを持っています。ページフォルトによってアボートする命令は、仮想記憶システムの要求と互換性のある手順でリスタートできます。リセット時はMMU機能は有効になっていないので、論理アドレスは物理メモリのアドレスに変換されません。 |

| 物理アドレス空間は、64Kバイトの論理アドレス空間(プログラムによって扱われる空間)をページに分割することで拡張されます。ページは、Z800マイクロプロセッサーのより広大な物理アドレス空間にマッピング(変換)されます。マッピングプロセスは、ユーザソフトウェアアドレスを物理メモリから切り離します。これによってユーザは、情報が物理メモリのどこに実際に保存されるかといったことを意識せずに済みます。ページの実際のサイズは、プログラム/データ分離モードが可能であるかどうかで決まります。もしそれが可能であれば、個々のページ長は8Kバイトとなり、可能でなければ4Kバイト長となります。ページマッピング技術によって、16ビット論理アドレスは、24ビット物理アドレスに変換されます(40ピンデバイスでは下位19ビットだけが外部利用可能です)。アドレス変換は、システムモードでもユーザーモードでも起こります。それは、それぞれのモードで使用される個別の変換機構によります。MMUはさらに、オペレーティングシステムの介入なしに、最大64Kバイトの範囲のプログラムが、最大64Kバイトのデータを操作できるように、命令参照をデータ参照から分離できるようにします。 |

|

|

| MMUアーキテクチャ |

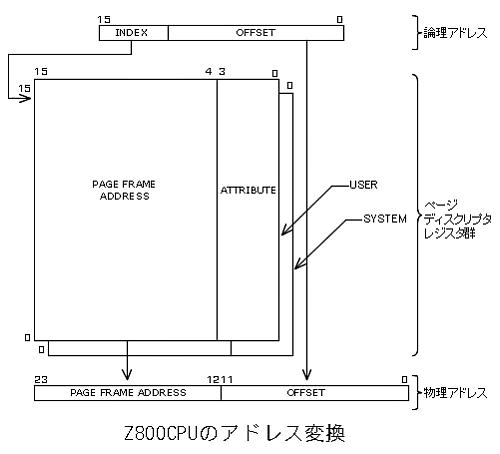

| Z800MMUは、アドレス変換に使用される2セットの16ページディスクリプタレジスタ(下図)、変換機構を管理する16ビット制御レジスタ、ページディスクリプタレジスタポインタ、ページディスクリプタのセットを無効化するためのI/Oライトオンリーポート、ページディスクリプタレジスタにアクセスするための2本のI/Oポートから成っています。一方のページディスクリプタレジスタのセットはシステムモード専用で、もう一方のセットはユーザーモード専用です。 |

| アドレスの変換中、アトリビュートは位置がチェックされる論理ページと関連づけられます。最終的なな論理ページはCPUモード(ユーザまたはシステム)、アドレス空間(プログラム/データ)、および論理アドレスの4つのMSB(Most Significant Bit)によって決定されます。ページには、タスクの実行によって書き換えられるのを防ぐためにライトプロテクトをかけることができます。そしてまた情報が後の参照のためキャッシュにコピーされるのを防ぐために「非キャッシュマーク」をつけることができます。後者の機能は、プロセッサが複数のデバイス間で共有される情報の常に最新のバージョンにアクセスすることを保証するもので、マルチプロセッサシステムで有効な機能です。MMUは、ページが変更されたかどうかを示すそれぞれのページに対応するビットも管理します。 |

| 各ページディスクリプタレジスタはValidビットを持っていて、それはそのディスクリプタが有効な情報を含んでいることを示しています。MMUは無効なディスクリプタがページフォールトを発生させることを利用してアドレスを変換する場合があります。ページディスクリプタレジスタのグループのValidビットは、MMU制御ポートへのライトによってリセットされます。 |

|

|

|

| CPUオペレーションの各モードのために、MMUは命令フェッチとデータフェッチを分離するよう設定できるようになっています。このように、プログラムアドレス空間はデータアドレス空間と分離されるのです。プログラム/データ分離モードが有効なとき、オペレーションの現在のCPUモード(ユーザまたはシステム)の16ページディスクリプタレジスタは2つのセットに分割されます。ひとつは命令フェッチのためのもので、もうひとつはデータフェッチのためのものです。プログラムカウンタ相対アドレッシングモードを使った命令フェッチあるいはデータアクセスは、プログラムアドレス空間側のMMUレジスタ群によって変換されます。それ以外のアドレッシングモードを使ったデータアクセス、および割り込みモード2での割り込みベクタテーブルへのアクセスはデータアドレス空間側のMMUレジスタ群を使用します。MMUオペレーションのこのモードにおいては、ページサイズは8192バイトです。CPUオペレーションのユーザおよびシステムモードが別々のプログラムアドレス空間とデータアドレス空間を持っているかどうかを指定するMMUマスターコントロールレジスタには2本の制御ビットがあります。 |

| 各16ビットページディスクリプタレジスタには、4ビットのアトリビュートフィールドと12ビットのページフレームアドレスフィールドがあります。このアトリビュートフィールドはディスクリプタのLSB(Least Significant Bit)と重複しており、以下の4本の制御および状態ビットが含まれています。 |

| Modified (M) -書き換えビット. このビットは、このページ内の論理アドレスに対して書き込みが正常に行われると常に自動的にセットされます。そしてこのディスクリプタレジスタを読み込むソフトウェアルーチンのみが0にクリアできるのです。 |

| Cacheable (C) -キャッシュ可能ビット. このビットが1にセットされていると、このページからフェッチされた情報はキャッシュの中に蓄えられます。反対に0にクリアされていると、キャッシュ制御メカニズムは、その情報のコピーがキャッシュ内に保持されないように働きます。 |

| Write-Protect (WP) -書き込み禁止ビット. このビットが1にセットされていると、このページ内の論理アドレスにCPUが書き込みを行おうとしたときページフォールトが発生し、それ以降の書き込み操作を抑制します。0にクリアされていた場合は、すべての正当なアクセスが許可されます。 |

| Valid (V) -有効ビット. このビットが1にセットされていると、このディスクリプタは正当な情報を含んでいます。0にクリアされていると、このページ内の論理アドレスへのすべてのCPUのアクセスがページフォールトの原因となります。 |

|

|

| MMUコントロールレジスタとI/Oポート |

| MMUの動作は一本の制御レジスタと4つの専用I/Oポートによってコントロールされます。MMUマスターコントロールレジスタ(下図)は、ユーザモードとシステムモードにおいて事実上プログラム/データアドレス空間の分離を決定します。これは、ユーザおよびシステムモードにおいて生成される論理アドレスが、MMUにより変換されるかどうかは関係ありません。ページディスクリプタレジスタは、ページディスクリプタレジスタポインタに入っているレジスタアドレスを介して間接的にアクセスされます。ディスクリプタセレクトポートは、ページディスクリプタレジスタポインタが指すページディスクリプタレジスタにアクセスするために使用されます。このアクセスの後、ページディスクリプタレジスタポインタが変更されることはありません。ブロック移動I/Oポートは、ページディスクリプタレジスタとメモリ間でワード単位のブロック移動に使用され、このI/Oポートへの書き込みまたは参照は、ページディスクリプタレジスタポインタで指されるデータへのアクセスになり、そのポインタはひとつインクリメントされます。無効化I/Oポートは、ページディスクリプタレジスタのブロックを無効にするために使用され、このポートへの書き込みはページディスクリプタレジスタの選択されたブロック内のValidビットを0にクリアします。 |

|

15

|

5

|

4

|

0

|

|

|

|

UTE

|

UPD

|

0

|

0

|

STE

|

SPD

|

0

|

0

|

0

|

0

|

0

|

PFI

|

|

|

|

|

|

|

MMUマスターコントロールレジスタ

|

|

|

| MMUマスターコントロールレジスタ |

| MMUマスターコントロールレジスタはMMUの動作をコントロールします。このレジスタには4本のビットがあり、このレジスタ内の他のビットはすべて0にクリアされている必要があります。MMUマスターコントロールレジスタの4本のビットの詳細は以下のとおりです。 |

| ページフォールト識別子(PFI) この5ビットのフィールドは、アクセス違反が検出されたときにどちらのページディスクリプタレジスタがアクセスされていたかを示す情報をラッチします。 |

| システムモード・プログラム/データ分離イネーブル(SPD) このビットが1にセットされていると、命令のフェッチとPC相対アドレッシングモードでのデータアクセスは、システムモードのページディスクリプタレジスタの8~15ビットを使用し、PC相対アドレッシングモードを使わないデータ参照では、システムモードのページディスクリプタレジスタの0~7ビットを使用します。このビットが0にクリアされていると、システムモードのページディスクリプタレジスタの0~15ビットが命令とデータの参照の変換に使用されます。 |

| システムモード変換イネーブル(STE) このビットが1にセットされていると、システムモードで生成された論理アドレスが変換されます。このビットが0にクリアされていると、アドレスはMSBの中が0拡張されたMMUをすり抜けます。アトリビュートのチェックをしないか、書き換えビット(M)がセットされているか |

| ユーザモード・プログラム/データ分離イネーブル(UPD) このビットが1にセットされていると、命令のフェッチとPC相対アドレッシングモードでのデータアクセスは、ユーザモードのページディスクリプタレジスタの8~15ビットを使用し、PC相対アドレッシングモードを使わないデータ参照では、ユーザモードのページディスクリプタレジスタの0~7ビットを使用します。このビットが0にクリアされていると、ユーザモードのページディスクリプタレジスタの0~15ビットが命令とデータの参照の変換に使用されます。 |

| ユーザモード変換イネーブル(UTE) このビットが1にセットされていると、ユーザモードで生成された論理アドレスが変換されます。このビットが0にクリアされていると、アドレスはMSBの中が0拡張されたMMUをすり抜けます。アトリビュートのチェックをしないか、書き換えビット(M)がセットされているか |

| ページディスクリプタレジスタポインタ |

| MMUページディスクリプタレジスタの中へ、および外へのデータ移動には、ページディスクリプタレジスタポインタを使います。この8ビットのレジスタにはページディスクリプタレジスタのひとつのアドレスが入ります。ワードI/O命令が、I/OアドレスFFxxF5(ディスクリプタ選択ポート)にアクセスすると、このレジスタはページディスクリプタレジスタへのアクセスに使用されます。ワードI/O命令が、I/OアドレスFFxxF4(ブロック移動I/Oポート)にアクセスすると、このレジスタもまたページディスクリプタレジスタへのアクセスに使用されます。が、このアクセスの後、このレジスタは自動的にひとつインクリメントされます。 |

| ディスクリプタ選択ポート |

| ページディスクリプタレジスタの中へ、および外への1ワードの移動は、FFxxF5番地にあるこの専用のI/Oポートにライトまたはリードすることによって行われます。ページディスクリプタレジスタポインタが正しく初期化されていれば、いくつかのワードI/O命令はこのポートによってページディスクリプタレジスタにアクセスするために使用され得る。 |

| ブロック移動I/Oポート |

| ページディスクリプタレジスタの中へ、および外へのブロック移動は、FFxxF4番地にあるこの専用のI/Oポートにライトまたはリードすることによって行われます。ページディスクリプタレジスタポインタが正しく初期化されていれば、いくつかのワードI/O命令はこのポートによってページディスクリプタレジスタにアクセスするために使用され得る。 |

| 無効化I/Oポート |

| Validビットは、この専用の8ビットポートにライトすることでクリアできます(すなわち、ページディスクリプタレジスタはこの操作によって無効化されます)(次表参照)。個々のValidビットは、後でページディスクリプタレジスタにソフトウェアによってライトされることでセットされます。このI/Oポートをリードすることにより返される値は不定です。 |

|

無効化ポート表

|

|

|

|

コード

|

無効レジスタ

|

|

|

|

|

01H

|

|

システムページディスクリプタレジスタ 0-7 |

|

02H

|

|

システムページディスクリプタレジスタ 8-15 |

|

03H

|

|

システムページディスクリプタレジスタ 0-15 |

|

04H

|

|

ユーザページディスクリプタレジスタ 0-7 |

|

05H

|

|

ユーザページディスクリプタレジスタ 8-15 |

|

08H

|

|

ユーザページディスクリプタレジスタ 8-15 |

|

0CH

|

|

ユーザページディスクリプタレジスタ 0-15 |

|

|

|

|

|

|

| 変換メカニズム |

| アドレス変換 |

| アドレス変換の様子を下図に示します。プログラム/データ空間分離ビットが0でクリアされている場合、16ビットの論理アドレスは2つのフィールドに分割されます。4ビットのインデックスフィールドは16ページディスクリプタレジスタのひとつを選択するために使用され、12ビットのオフセットフィールドは、物理アドレスの下位12ビットとなります。物理アドレスは、選択されたページディスクリプタレジスタにより与えられる12ビットのページフレームアドレスと論理アドレスにより与えられる12ビットオフセットの合成により作られます。 |

| アドレス変換の様子を下図に示します。プログラム/データ空間分離ビットが1にセットされている場合は、論理アドレスは3ビットのインデックスフィールドと13ビットのオフセットフィールドに分割されます。そのページディスクリプタレジスタは11ビットのページフレームアドレスフィールドからなります。物理アドレスは、そのページフレームアドレスと論理オフセットの結合の結果になります。ページディスクリプタレジスタは、CPUのプログラム/データアドレスビット1本と論理アドレスの3本のインデックスビットからなる4ビットのインデックスフィールドにより選択されます。 |

※クリックすると拡大されます。

|

|